# **PCA9517A**

# Level translating I<sup>2</sup>C-bus repeater

Rev. 4.1 — 24 May 2016

**Product data sheet**

# 1. General description

The PCA9517A is a CMOS integrated circuit that provides level shifting between low voltage (down to 0.9 V) and higher voltage (2.7 V to 5.5 V) I<sup>2</sup>C-bus or SMBus applications. While retaining all the operating modes and features of the I<sup>2</sup>C-bus system during the level shifts, it also permits extension of the I<sup>2</sup>C-bus by providing bidirectional buffering for both the data (SDA) and the clock (SCL) lines, thus enabling two buses of 400 pF. Using the PCA9517A enables the system designer to isolate two halves of a bus for both voltage and capacitance. The SDA and SCL pins are overvoltage tolerant and are high-impedance when the PCA9517A is unpowered.

The 2.7 V to 5.5 V bus port B drivers behave much like the drivers on the PCA9515A device, while the adjustable voltage bus port A drivers drive more current and eliminate the static offset voltage. This results in a LOW on the port B translating into a nearly 0 V LOW on the port A which accommodates smaller voltage swings of lower voltage logic.

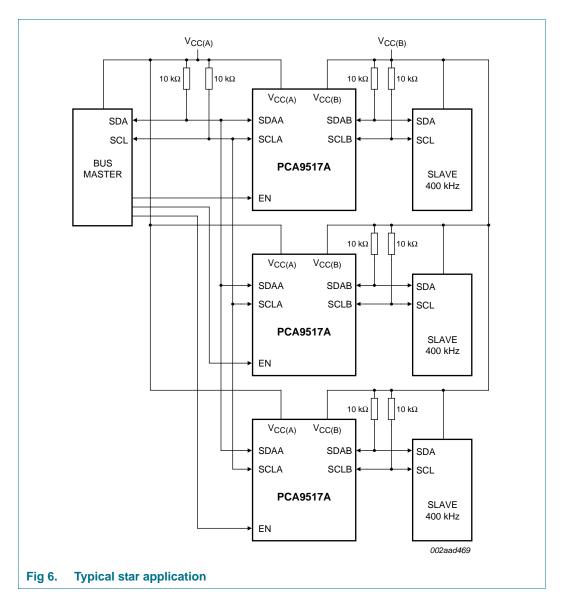

The static offset design of the port B PCA9517A I/O drivers prevent them from being connected to another device that has rise time accelerator including the PCA9510, PCA9511, PCA9512, PCA9513, PCA9514, PCA9515A, PCA9516A, PCA9517A (port B), or PCA9518. Port A of two or more PCA9517As can be connected together, however, to allow a star topography with port A on the common bus, and port A can be connected directly to any other buffer with static or dynamic offset voltage. Multiple PCA9517As can be connected in series, port A to port B, with no build-up in offset voltage with only time of flight delays to consider.

The PCA9517A drivers are not enabled unless  $V_{CC(A)}$  is above 0.8 V and  $V_{CC(B)}$  is above 2.5 V. The EN pin can also be used to turn the drivers on and off under system control. Caution should be observed to only change the state of the enable pin when the bus is idle.

The output pull-down on the port B internal buffer LOW is set for approximately 0.5 V, while the input threshold of the internal buffer is set about 70 mV lower (0.43 V). When the port B I/O is driven LOW internally, the LOW is not recognized as a LOW by the input. This prevents a lock-up condition from occurring. The output pull-down on port A drives a hard LOW and the input level is set at  $0.3V_{\rm CC(A)}$  to accommodate the need for a lower LOW level in systems where the low voltage side supply voltage is as low as 0.9 V.

Table 1. PCA9517 and PCA9517A comparison

| Parameter                    | PCA9517[1] | PCA9517A[2] |

|------------------------------|------------|-------------|

| electrostatic discharge, HBM | > 2 kV     | > 5.5 kV    |

- [1] PCA9517 will be discontinued in several years, so move to the PCA9517A for all new designs and system updates.

- 2] The PCA9517A is an improved hot swap and ESD version of the PCA9517, but otherwise operates identically and should be used for all new designs and system updates.

Level translating I<sup>2</sup>C-bus repeater

## 2. Features and benefits

- 2 channel, bidirectional buffer isolates capacitance and allows 400 pF on either side of the device

- Voltage level translation from 0.9 V to 5.5 V and from 2.7 V to 5.5 V

- Footprint and functional replacement for PCA9515/15A

- I<sup>2</sup>C-bus and SMBus compatible

- Active HIGH repeater enable input

- Open-drain input/outputs

- Lock-up free operation

- Supports arbitration and clock stretching across the repeater

- Accommodates Standard-mode and Fast-mode I<sup>2</sup>C-bus devices and multiple masters

- Powered-off high-impedance I<sup>2</sup>C-bus pins

- Port A operating supply voltage range of 0.9 V to 5.5 V

- Port B operating supply voltage range of 2.7 V to 5.5 V

- 5 V tolerant I<sup>2</sup>C-bus and enable pins

- 0 Hz to 400 kHz clock frequency (the maximum system operating frequency may be less than 400 kHz because of the delays added by the repeater)

- ESD protection exceeds 5500 V HBM per JESD22-A114 and 1000 V CDM per JESD22-C101

- Latch-up testing is done to JEDEC Standard JESD78 which exceeds 100 mA

- Packages offered: SO8, TSSOP8 and HWSON8

# 3. Ordering information

Table 2. Ordering information

$T_{amb} = -40 \, ^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ .

| Type number   | Topside   | Package      | Package Package                                                                                                   |           |  |  |  |  |  |  |  |

|---------------|-----------|--------------|-------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|--|--|

|               | mark Name |              | ne Description                                                                                                    |           |  |  |  |  |  |  |  |

| PCA9517AD     | PA9517A   | SO8          | plastic small outline package; 8 leads; body width 3.9 mm                                                         | SOT96-1   |  |  |  |  |  |  |  |

| PCA9517ADP    | 9517A     | TSSOP8[1]    | plastic thin shrink small outline package; 8 leads; body width 3 mm                                               | SOT505-1  |  |  |  |  |  |  |  |

| PCA9517ADP/DG | 9517A     | TSSOP8[1][2] | plastic thin shrink small outline package; 8 leads; body width 3 mm                                               | SOT505-1  |  |  |  |  |  |  |  |

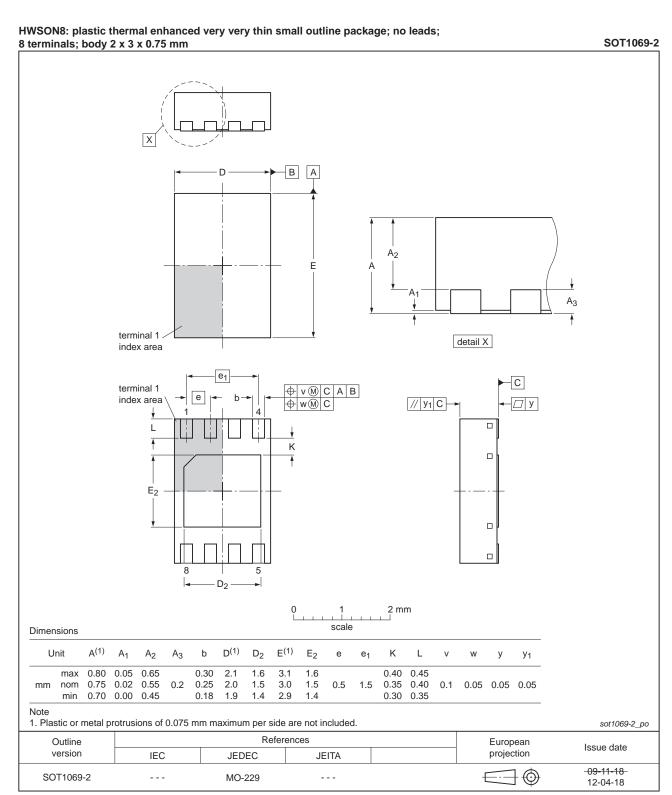

| PCA9517ATP    | 17A       | HWSON8       | plastic thermal enhanced very very thin small outline package; no leads; 8 terminals; body $2\times3\times0.8$ mm | SOT1069-2 |  |  |  |  |  |  |  |

- [1] Also known as MSOP8.

- [2] PCA9517ADP/DG is functionally the same (electrically and mechanically) as the PCA9517ADP, but was initially produced (e.g., "born") with Dark Green (lead-free and halogen/antimony-free) package material and is a temporary unique orderable part number for customers who desire to order and only receive Dark Green package material. The standard part PCA9517ADP will transition to Dark Green package material in 2Q'12 and then the PCA9517ADP and PCA9517ADP/DG devices will be identical. The PCA9517ADP/DG part number will be EOL after several years as customers who used this temporary part number update their BOM to the normal part number.

PCA9517A

Level translating I<sup>2</sup>C-bus repeater

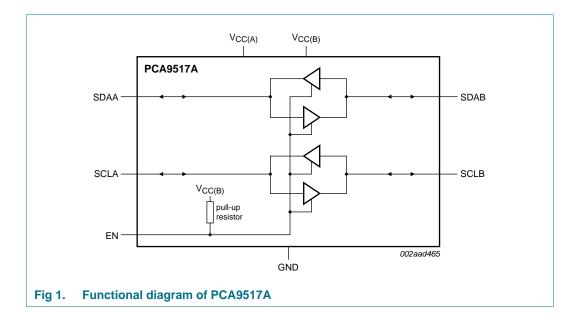

# 4. Functional diagram

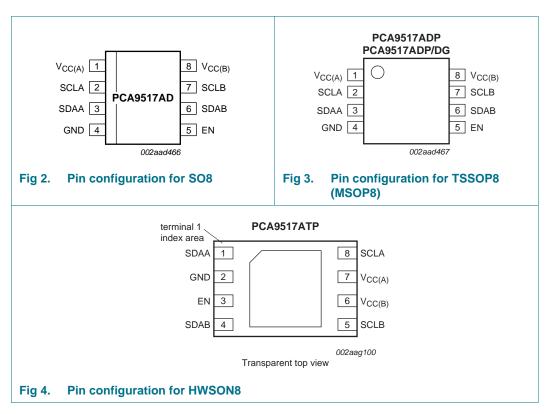

# 5. Pinning information

# 5.1 Pinning

Level translating I<sup>2</sup>C-bus repeater

## 5.2 Pin description

Table 3. Pin description

| Symbol             | Pin            |      | Description                            |

|--------------------|----------------|------|----------------------------------------|

|                    | SO8,<br>TSSOP8 |      |                                        |

| V <sub>CC(A)</sub> | 1              | 7    | port A supply voltage (0.9 V to 5.5 V) |

| SCLA               | 2              | 8    | serial clock port A bus                |

| SDAA               | 3              | 1    | serial data port A bus                 |

| GND                | 4              | 2[1] | supply ground (0 V)                    |

| EN                 | 5              | 3    | active HIGH repeater enable input      |

| SDAB               | 6              | 4    | serial data port B bus                 |

| SCLB               | 7              | 5    | serial clock port B bus                |

| V <sub>CC(B)</sub> | 8              | 6    | port B supply voltage (2.7 V to 5.5 V) |

<sup>[1]</sup> HWSON8 package die supply ground is connected to both GND pin and exposed center pad. GND pin must be connected to supply ground for proper device operation. For enhanced thermal, electrical, and board level performance, the exposed pad needs to be soldered to the board using a corresponding thermal pad on the board and for proper head conduction through the board, thermal vias need to be incorporated in the printed-circuit board in the thermal pad region.

# 6. Functional description

Refer to Figure 1 "Functional diagram of PCA9517A".

The PCA9517A enables  $I^2C$ -bus or SMBus translation down to  $V_{CC(A)}$  as low as 0.9 V without degradation of system performance. The PCA9517A contains two bidirectional open-drain buffers specifically designed to support up-translation/down-translation between the low voltage (as low as 0.9 V) and a 3.3 V or 5 V I<sup>2</sup>C-bus or SMBus. All inputs and I/Os are overvoltage tolerant to 5.5 V even when the device is unpowered (V<sub>CC(B)</sub> and/or V<sub>CC(A)</sub> = 0 V). The PCA9517A includes a power-up circuit that keeps the output drivers turned off until  $V_{CC(B)}$  is above 2.5 V and the  $V_{CC(A)}$  is above 0.8 V.  $V_{CC(B)}$  and V<sub>CC(A)</sub> can be applied in any sequence at power-up. After power-up and with the enable (EN) HIGH, a LOW level on port A (below 0.3V<sub>CC(A)</sub>) turns the corresponding port B driver (either SDA or SCL) on and drives port B down to about 0.5 V. When port A rises above 0.3V<sub>CC(A)</sub>, the port B pull-down driver is turned off and the external pull-up resistor pulls the pin HIGH. When port B falls first and goes below 0.4 V the port A driver is turned on and port A pulls down to 0 V. The port A pull-down is not enabled unless the port B voltage goes below 0.4 V. If the port B low voltage goes below 0.4 V, the port B pull-down driver is enabled and port B will only be able to rise to 0.5 V until port A rises above 0.3V<sub>CC(A)</sub>, then port B will continue to rise being pulled up by the external pull-up resistor. The V<sub>CC(A)</sub> is only used to provide the 0.3V<sub>CC(A)</sub> reference to the port A input comparators and for the power good detect circuit. The PCA9517A logic and all I/Os are powered by the V<sub>CC(B)</sub> pin.

Level translating I<sup>2</sup>C-bus repeater

#### 6.1 Enable

The EN pin is active HIGH with an internal pull-up to  $V_{CC(B)}$  and allows the user to select when the repeater is active. This can be used to isolate a badly behaved slave on power-up until after the system power-up reset. It should never change state during an  $I^2C$ -bus operation because disabling during a bus operation will hang the bus and enabling part way through a bus cycle could confuse the  $I^2C$ -bus parts being enabled.

The enable pin should only change state when the global bus and the repeater port are in an idle state to prevent system failures.

# 6.2 I<sup>2</sup>C-bus systems

As with the standard I<sup>2</sup>C-bus system, pull-up resistors are required to provide the logic HIGH levels on the buffered bus (standard open-collector configuration of the I<sup>2</sup>C-bus). The size of these pull-up resistors depends on the system, but each side of the repeater must have a pull-up resistor. This part designed to work with Standard mode and Fast mode I<sup>2</sup>C-bus devices in addition to SMBus devices. Standard mode I<sup>2</sup>C-bus devices only specify 3 mA output drive; this limits the termination current to 3 mA in a generic I<sup>2</sup>C-bus system where Standard-mode devices and multiple masters are possible. Under certain conditions higher termination currents can be used.

Please see Application Note AN255, I<sup>2</sup>C/SMBus Repeaters, Hubs and Expanders for additional information on sizing resistors and precautions when using more than one PCA9517A in a system or using the PCA9517A in conjunction with other bus buffers.

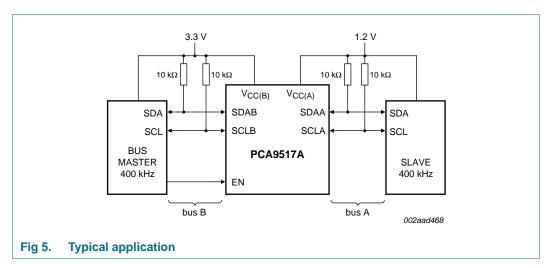

# 7. Application design-in information

A typical application is shown in Figure 5. In this example, the system master is running on a  $3.3 \text{ V I}^2\text{C}$ -bus while the slave is connected to a 1.2 V bus. Both buses run at 400 kHz. Master devices can be placed on either bus.

The PCA9517A is 5 V tolerant, so it does not require any additional circuitry to translate between 0.9 V to 5.5 V bus voltages and 2.7 V to 5.5 V bus voltages.

#### Level translating I<sup>2</sup>C-bus repeater

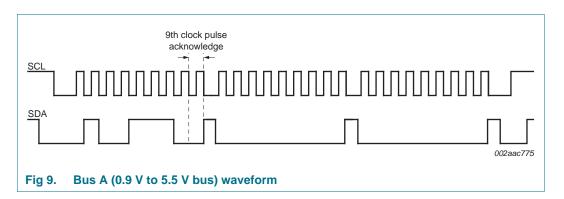

When port A of the PCA9517A is pulled LOW by a driver on the  $I^2C$ -bus, a comparator detects the falling edge when it goes below  $0.3V_{CC(A)}$  and causes the internal driver on port B to turn on, causing port B to pull down to about 0.5 V. When port B of the PCA9517A falls, first a CMOS hysteresis type input detects the falling edge and causes the internal driver on port A to turn on and pull the port A pin down to ground. In order to illustrate what would be seen in a typical application, refer to Figure 9 and Figure 10. If the bus master in Figure 5 were to write to the slave through the PCA9517A, waveforms shown in Figure 9 would be observed on the A bus. This looks like a normal  $I^2C$ -bus transmission except that the HIGH level may be as low as 0.9 V, and the turn on and turn off of the acknowledge signals are slightly delayed.

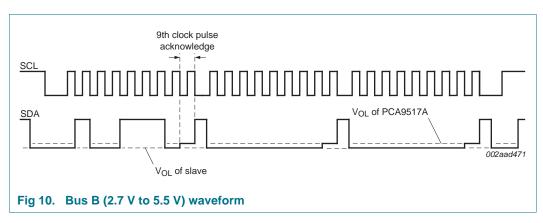

On the B bus side of the PCA9517A, the clock and data lines would have a positive offset from ground equal to the  $V_{OL}$  of the PCA9517A. After the eighth clock pulse, the data line will be pulled to the  $V_{OL}$  of the slave device which is very close to ground in this example. At the end of the acknowledge, the level rises only to the LOW level set by the driver in the PCA9517A for a short delay while the A bus side rises above  $0.3V_{CC(A)}$  then it continues HIGH. It is important to note that any arbitration or clock stretching events require that the LOW level on the B bus side at the input of the PCA9517A ( $V_{IL}$ ) be at or below 0.4 V to be recognized by the PCA9517A and then transmitted to the A bus side.

Multiple PCA9517A port A sides can be connected in a star configuration (Figure 6), allowing all nodes to communicate with each other.

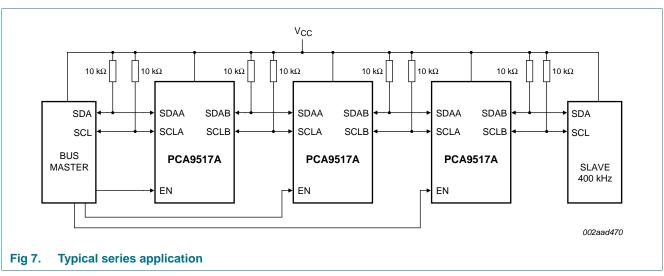

Multiple PCA9517As can be connected in series (<u>Figure 7</u>) as long as port A is connected to port B. I<sup>2</sup>C-bus slave devices can be connected to any of the bus segments. The number of devices that can be connected in series is limited by repeater delay/time-of-flight considerations on the maximum bus speed requirements.

# Level translating I<sup>2</sup>C-bus repeater

PCA9517A

All information provided in this document is subject to legal disclaimers.

# Level translating I<sup>2</sup>C-bus repeater

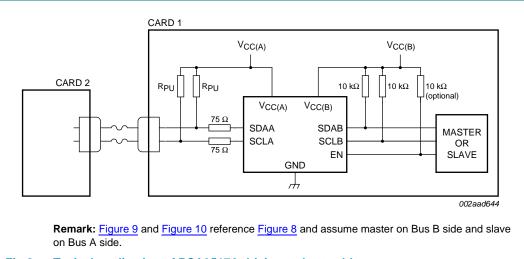

Fig 8. Typical application of PCA9517A driving a short cable

Level translating I<sup>2</sup>C-bus repeater

# 8. Limiting values

#### Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol             | Parameter                      | Conditions                                        | Min  | Max  | Unit |

|--------------------|--------------------------------|---------------------------------------------------|------|------|------|

| V <sub>CC(B)</sub> | supply voltage port B          | 2.7 V to 5.5 V                                    | -0.5 | +7   | V    |

| V <sub>CC(A)</sub> | supply voltage port A          | adjustable                                        | -0.5 | +7   | V    |

| V <sub>I/O</sub>   | voltage on an input/output pin | port A and port B; enable pin (EN)                | -0.5 | +7   | V    |

| I <sub>I/O</sub>   | input/output current           | port A; port B                                    | -    | 50   | mA   |

| l <sub>l</sub>     | input current                  | EN, V <sub>CC(A)</sub> , V <sub>CC(B)</sub> , GND | -    | 50   | mA   |

| P <sub>tot</sub>   | total power dissipation        |                                                   | -    | 100  | mW   |

| T <sub>stg</sub>   | storage temperature            |                                                   | -55  | +125 | °C   |

| T <sub>amb</sub>   | ambient temperature            | operating in free air                             | -40  | +85  | °C   |

| Tj                 | junction temperature           |                                                   | -    | +125 | °C   |

Level translating I<sup>2</sup>C-bus repeater

# 9. Static characteristics

# Table 5. Static characteristics

$V_{CC}$  = 2.7 V to 5.5 V; GND = 0 V;  $T_{amb}$  = -40 °C to +85 °C; unless otherwise specified.

| Symbol                            | Parameter                                                                  | Conditions                                                                                             |     | Min                   | Тур  | Max                    | Unit |

|-----------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|-----------------------|------|------------------------|------|

| Supplies                          |                                                                            |                                                                                                        |     |                       |      |                        |      |

| V <sub>CC(B)</sub>                | supply voltage port B                                                      |                                                                                                        |     | 2.7                   | -    | 5.5                    | V    |

| V <sub>CC(A)</sub>                | supply voltage port A                                                      |                                                                                                        | [1] | 0.9                   | -    | 5.5                    | V    |

| I <sub>CC(VCC(A))</sub>           | supply current on pin V <sub>CC(A)</sub>                                   |                                                                                                        |     | -                     | -    | 1                      | mA   |

| I <sub>CCH</sub>                  | HIGH-level supply current                                                  | both channels HIGH;<br>$V_{CC} = 5.5 \text{ V}$ ;<br>$SDAn = SCLn = V_{CC}$                            |     | -                     | 1.5  | 5                      | mA   |

| I <sub>CCL</sub>                  | LOW-level supply current                                                   | both channels LOW;<br>V <sub>CC</sub> = 5.5 V;<br>one SDA and one SCL = GND;<br>other SDA and SCL open |     | -                     | 1.5  | 5                      | mA   |

| I <sub>CC(A)c</sub>               | contention port A supply current                                           | V <sub>CC</sub> = 5.5 V;<br>SDAn = SCLn = V <sub>CC</sub>                                              |     | -                     | 1.5  | 5                      | mA   |

| Input and                         | output SDAB and SCLB                                                       |                                                                                                        |     |                       |      |                        |      |

| $V_{IH}$                          | HIGH-level input voltage                                                   |                                                                                                        |     | 0.7V <sub>CC(B)</sub> | -    | 5.5                    | V    |

| $V_{IL}$                          | LOW-level input voltage                                                    |                                                                                                        | [2] | -0.5                  | -    | +0.3V <sub>CC(B)</sub> | V    |

| V <sub>ILc</sub>                  | contention LOW-level input voltage                                         |                                                                                                        |     | -0.5                  | 0.4  | -                      | V    |

| V <sub>IK</sub>                   | input clamping voltage                                                     | I <sub>I</sub> = -18 mA                                                                                |     | -                     | -    | -1.2                   | V    |

| I <sub>LI</sub>                   | input leakage current                                                      | V <sub>I</sub> = 3.6 V                                                                                 |     | -                     | -    | ±1                     | μΑ   |

| I <sub>IL</sub>                   | LOW-level input current                                                    | SDA, SCL; V <sub>I</sub> = 0.2 V                                                                       |     | -                     | -    | 10                     | μΑ   |

| V <sub>OL</sub>                   | LOW-level output voltage                                                   | I <sub>OL</sub> = 100 μA or 6 mA                                                                       |     | 0.47                  | 0.52 | 0.6                    | V    |

| V <sub>OL</sub> -V <sub>ILc</sub> | difference between LOW-level output and LOW-level input voltage contention | guaranteed by design                                                                                   |     | -                     | -    | 70                     | mV   |

| I <sub>LOH</sub>                  | HIGH-level output leakage current                                          | V <sub>O</sub> = 3.6 V                                                                                 |     | -                     | -    | 10                     | μΑ   |

| C <sub>io</sub>                   | input/output capacitance                                                   | $V_1 = 3 \text{ V or } 0 \text{ V}; V_{CC} = 3.3 \text{ V}$                                            |     | -                     | 6    | 7                      | pF   |

|                                   |                                                                            | $V_{I} = 3 \text{ V or } 0 \text{ V}; V_{CC} = 0 \text{ V}$                                            |     | -                     | 6    | 7                      | pF   |

| Input and                         | output SDAA and SCLA                                                       |                                                                                                        |     |                       |      |                        | -    |

| V <sub>IH</sub>                   | HIGH-level input voltage                                                   |                                                                                                        |     | 0.7V <sub>CC(A)</sub> | -    | 5.5                    | V    |

| V <sub>IL</sub>                   | LOW-level input voltage                                                    |                                                                                                        | [3] | -0.5                  | -    | +0.3V <sub>CC(A)</sub> | V    |

| V <sub>IK</sub>                   | input clamping voltage                                                     | I <sub>I</sub> = -18 mA                                                                                |     | -                     | -    | -1.2                   | V    |

| ILI                               | input leakage current                                                      | V <sub>I</sub> = 3.6 V                                                                                 |     | -                     | -    | ±1                     | μΑ   |

| I <sub>IL</sub>                   | LOW-level input current                                                    | SDA, SCL; V <sub>I</sub> = 0.2 V                                                                       |     | -                     | -    | 10                     | μΑ   |

| V <sub>OL</sub>                   | LOW-level output voltage                                                   | I <sub>OL</sub> = 6 mA                                                                                 |     | -                     | 0.1  | 0.2                    | V    |

| I <sub>LOH</sub>                  | HIGH-level output leakage current                                          | V <sub>O</sub> = 3.6 V                                                                                 |     | -                     | -    | 10                     | μΑ   |

| C <sub>io</sub>                   | input/output capacitance                                                   | $V_{I} = 3 \text{ V or } 0 \text{ V}; V_{CC} = 3.3 \text{ V}$                                          |     | -                     | 6    | 7                      | pF   |

|                                   |                                                                            | $V_{I} = 3 \text{ V or } 0 \text{ V}; V_{CC} = 0 \text{ V}$                                            |     | -                     | 6    | 7                      | pF   |

PCA9517A

All information provided in this document is subject to legal disclaimers.

Level translating I<sup>2</sup>C-bus repeater

Table 5. Static characteristics ... continued

$V_{CC}$  = 2.7 V to 5.5 V; GND = 0 V;  $T_{amb}$  = -40 °C to +85 °C; unless otherwise specified.

| Symbol              | Parameter                         | Conditions                                                | Min                   | Тур | Max                    | Unit |

|---------------------|-----------------------------------|-----------------------------------------------------------|-----------------------|-----|------------------------|------|

| Enable              |                                   |                                                           |                       |     |                        | _    |

| V <sub>IL</sub>     | LOW-level input voltage           |                                                           | -0.5                  | -   | +0.3V <sub>CC(B)</sub> | V    |

| V <sub>IH</sub>     | HIGH-level input voltage          |                                                           | 0.7V <sub>CC(B)</sub> | -   | 5.5                    | V    |

| I <sub>IL(EN)</sub> | LOW-level input current on pin EN | $V_1 = 0.2 \text{ V}, \text{ EN}; V_{CC} = 3.6 \text{ V}$ | -                     | -10 | -30                    | μΑ   |

| I <sub>LI</sub>     | input leakage current             |                                                           | -1                    | -   | +1                     | μΑ   |

| Ci                  | input capacitance                 | V <sub>I</sub> = 3.0 V or 0 V                             | -                     | 6   | 7                      | pF   |

<sup>[1]</sup> LOW-level supply voltage.

# 10. Dynamic characteristics

#### Table 6. Dynamic characteristics

$V_{CC} = 2.7 \text{ V to } 5.5 \text{ V}$ ; GND = 0 V;  $T_{amb} = -40 \text{ }^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ ; unless otherwise specified. [1][2]

| Symbol           | Parameter                          | Conditions                     |            | Min | Typ[3] | Max | Unit |

|------------------|------------------------------------|--------------------------------|------------|-----|--------|-----|------|

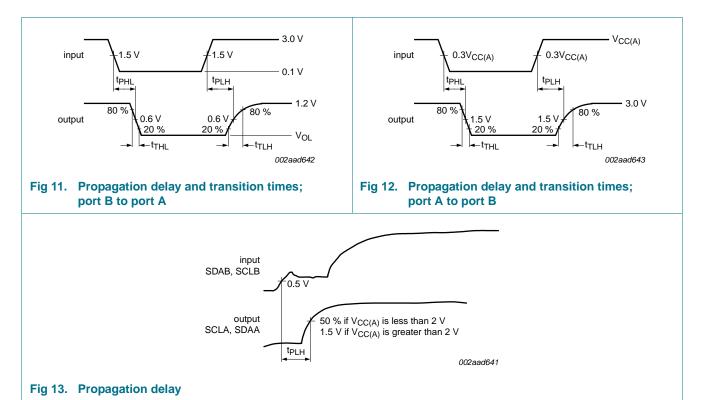

| t <sub>PLH</sub> | LOW to HIGH propagation delay      | port B to port A; Figure 13    | [4]        | 100 | 170    | 250 | ns   |

| t <sub>PHL</sub> | HIGH to LOW propagation delay      | port B to port A; Figure 11    |            |     |        |     |      |

|                  |                                    | $V_{CC(A)} \le 2.7 \text{ V}$  | <u>[5]</u> | 30  | 80     | 110 | ns   |

|                  |                                    | V <sub>CC(A)</sub> ≥ 3 V       |            | 10  | 66     | 300 | ns   |

| t <sub>TLH</sub> | LOW to HIGH output transition time | port A; Figure 11              |            | 10  | 20     | 30  | ns   |

| t <sub>THL</sub> | HIGH to LOW output transition time | port A; Figure 11              |            |     |        |     |      |

|                  |                                    | $V_{CC(A)} \le 2.7 \text{ V}$  | <u>[5]</u> | 1   | 77     | 105 | ns   |

|                  |                                    | V <sub>CC(A)</sub> ≥ 3 V       |            | 20  | 70     | 175 | ns   |

| t <sub>PLH</sub> | LOW to HIGH propagation delay      | port A to port B; Figure 12    | [6]        | 25  | 53     | 110 | ns   |

| t <sub>PHL</sub> | HIGH to LOW propagation delay      | port A to port B; Figure 12    | [6]        | 60  | 79     | 230 | ns   |

| t <sub>TLH</sub> | LOW to HIGH output transition time | port B; Figure 12              |            | 120 | 140    | 170 | ns   |

| t <sub>THL</sub> | HIGH to LOW output transition time | port B; Figure 12              |            | 30  | 48     | 90  | ns   |

| t <sub>su</sub>  | set-up time                        | EN HIGH before START condition | [7]        | 100 | -      | -   | ns   |

| t <sub>h</sub>   | hold time                          | EN HIGH after STOP condition   | [7]        | 100 | -      | -   | ns   |

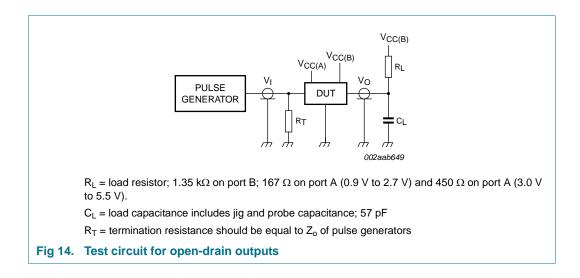

<sup>[1]</sup> Times are specified with loads of 1.35 kΩ pull-up resistance and 57 pF load capacitance on port B, and 167 Ω pull-up resistance and 57 pF load capacitance on port A. Different load resistance and capacitance will alter the RC time constant, thereby changing the propagation delay and transition times.

- [2] Pull-up voltages are  $V_{\text{CC}(A)}$  on port A and  $V_{\text{CC}(B)}$  on port B.

- [3] Typical values were measured with  $V_{CC(A)} = 3.3 \text{ V}$  at  $T_{amb} = 25 \,^{\circ}\text{C}$ , unless otherwise noted.

- [4] The t<sub>PLH</sub> delay data from port B to port A is measured at 0.5 V on port B to 0.5V<sub>CC(A)</sub> on port A when V<sub>CC(A)</sub> is less than 2 V, and 1.5 V on port A if V<sub>CC(A)</sub> is greater than 2 V.

- [5] Typical value measured with  $V_{CC(A)} = 2.7 \text{ V}$  at  $T_{amb} = 25 \,^{\circ}\text{C}$ .

- [6] The proportional delay data from port A to port B is measured at 0.3V<sub>CC(A)</sub> on port A to 1.5 V on port B.

- [7] The enable pin, EN, should only change state when the global bus and the repeater port are in an idle state.

PCA9517A

All information provided in this document is subject to legal disclaimers.

<sup>[2]</sup> V<sub>IL</sub> specification is for the first LOW level seen by the SDAB/SCLB lines. V<sub>ILC</sub> is for the second and subsequent LOW levels seen by the SDAB/SCLB lines.

<sup>[3]</sup> V<sub>IL</sub> for port A with envelope noise must be below 0.3V<sub>CC(A)</sub> for stable performance.

# Level translating I<sup>2</sup>C-bus repeater

#### 10.1 AC waveforms

# 11. Test information

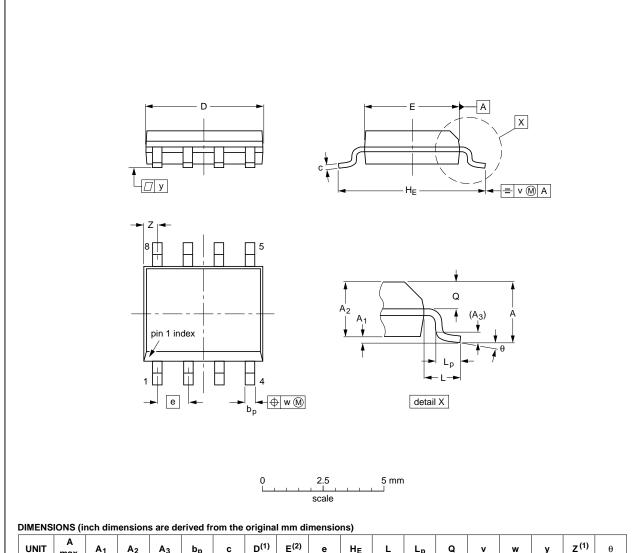

# 12. Package outline

#### SO8: plastic small outline package; 8 leads; body width 3.9 mm

SOT96-1

| UNIT   | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | А3   | bp           | С                | D <sup>(1)</sup> | E <sup>(2)</sup> | е    | HE             | L     | Lp             | ø              | ٧    | w    | у     | z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|------|--------------|------------------|------------------|------------------|------|----------------|-------|----------------|----------------|------|------|-------|------------------|----|

| mm     | 1.75      | 0.25<br>0.10   | 1.45<br>1.25   | 0.25 | 0.49<br>0.36 | 0.25<br>0.19     | 5.0<br>4.8       | 4.0<br>3.8       | 1.27 | 6.2<br>5.8     | 1.05  | 1.0<br>0.4     | 0.7<br>0.6     | 0.25 | 0.25 | 0.1   | 0.7<br>0.3       | 8° |

| inches | 0.069     | 0.010<br>0.004 | 0.057<br>0.049 | 0.01 |              | 0.0100<br>0.0075 | 0.20<br>0.19     | 0.16<br>0.15     | 0.05 | 0.244<br>0.228 | 0.041 | 0.039<br>0.016 | 0.028<br>0.024 | 0.01 | 0.01 | 0.004 | 0.028<br>0.012   | 0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

- 2. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

| OUTLINE |        | EUROPEAN | ISSUE DATE |  |            |                                 |

|---------|--------|----------|------------|--|------------|---------------------------------|

| VERSION | IEC    | JEDEC    | JEITA      |  | PROJECTION | 1330E DATE                      |

| SOT96-1 | 076E03 | MS-012   |            |  |            | <del>99-12-27</del><br>03-02-18 |

Fig 15. Package outline SOT96-1 (SO8)

PCA9517A

All information provided in this document is subject to legal disclaimers.

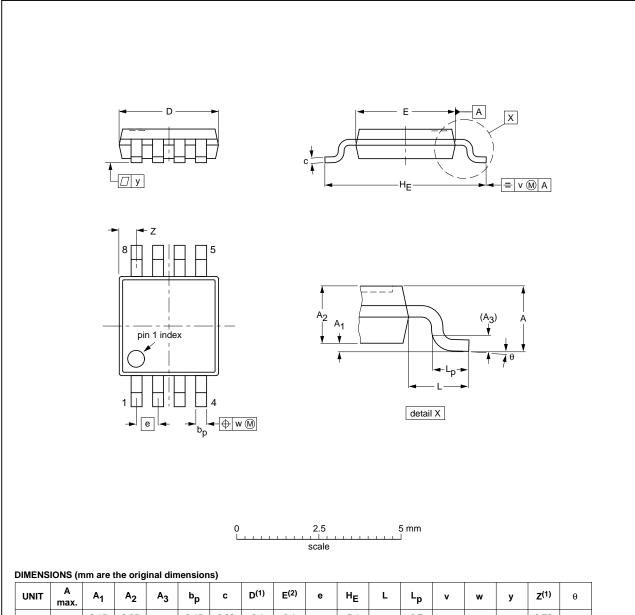

#### TSSOP8: plastic thin shrink small outline package; 8 leads; body width 3 mm

SOT505-1

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp           | C            | D <sup>(1)</sup> | E <sup>(2)</sup> | е    | HE         | L    | Lp         | v   | w   | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|----------------|--------------|--------------|------------------|------------------|------|------------|------|------------|-----|-----|-----|------------------|----------|

| mm   | 1.1       | 0.15<br>0.05   | 0.95<br>0.80   | 0.25           | 0.45<br>0.25 | 0.28<br>0.15 | 3.1<br>2.9       | 3.1<br>2.9       | 0.65 | 5.1<br>4.7 | 0.94 | 0.7<br>0.4 | 0.1 | 0.1 | 0.1 | 0.70<br>0.35     | 6°<br>0° |

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

|       |       |        | ISSUE DATE                      |

|-------|-------|--------|---------------------------------|

| JEDEC | JEITA | PROJEC | CTION                           |

|       |       |        | <del>99-04-09</del><br>03-02-18 |

|       |       |        |                                 |

Fig 16. Package outline SOT505-1 (TSSOP8)

All information provided in this document is subject to legal disclaimers.

Level translating I<sup>2</sup>C-bus repeater

Fig 17. Package outline SOT1069-2 (HWSON8)

PCA9517A

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2016. All rights reserved.

15 of 22

Level translating I<sup>2</sup>C-bus repeater

# 13. Soldering of SMD packages

This text provides a very brief insight into a complex technology. A more in-depth account of soldering ICs can be found in Application Note *AN10365* "Surface mount reflow soldering description".

# 13.1 Introduction to soldering

Soldering is one of the most common methods through which packages are attached to Printed Circuit Boards (PCBs), to form electrical circuits. The soldered joint provides both the mechanical and the electrical connection. There is no single soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and Surface Mount Devices (SMDs) are mixed on one printed wiring board; however, it is not suitable for fine pitch SMDs. Reflow soldering is ideal for the small pitches and high densities that come with increased miniaturization.

## 13.2 Wave and reflow soldering

Wave soldering is a joining technology in which the joints are made by solder coming from a standing wave of liquid solder. The wave soldering process is suitable for the following:

- Through-hole components

- Leaded or leadless SMDs, which are glued to the surface of the printed circuit board

Not all SMDs can be wave soldered. Packages with solder balls, and some leadless packages which have solder lands underneath the body, cannot be wave soldered. Also, leaded SMDs with leads having a pitch smaller than ~0.6 mm cannot be wave soldered, due to an increased probability of bridging.

The reflow soldering process involves applying solder paste to a board, followed by component placement and exposure to a temperature profile. Leaded packages, packages with solder balls, and leadless packages are all reflow solderable.

Key characteristics in both wave and reflow soldering are:

- · Board specifications, including the board finish, solder masks and vias

- · Package footprints, including solder thieves and orientation

- The moisture sensitivity level of the packages

- Package placement

- Inspection and repair

- Lead-free soldering versus SnPb soldering

#### 13.3 Wave soldering

Key characteristics in wave soldering are:

- Process issues, such as application of adhesive and flux, clinching of leads, board transport, the solder wave parameters, and the time during which components are exposed to the wave

- Solder bath specifications, including temperature and impurities

PCA9517A

Level translating I<sup>2</sup>C-bus repeater

# 13.4 Reflow soldering

Key characteristics in reflow soldering are:

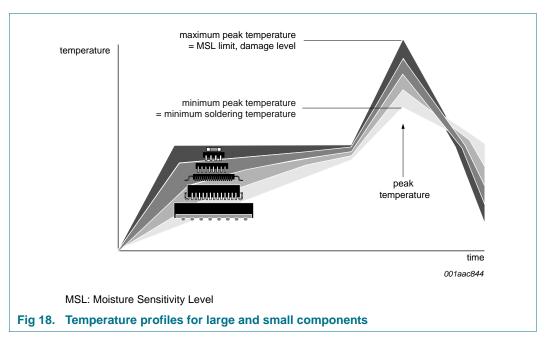

- Lead-free versus SnPb soldering; note that a lead-free reflow process usually leads to higher minimum peak temperatures (see <u>Figure 18</u>) than a SnPb process, thus reducing the process window

- Solder paste printing issues including smearing, release, and adjusting the process window for a mix of large and small components on one board

- Reflow temperature profile; this profile includes preheat, reflow (in which the board is heated to the peak temperature) and cooling down. It is imperative that the peak temperature is high enough for the solder to make reliable solder joints (a solder paste characteristic). In addition, the peak temperature must be low enough that the packages and/or boards are not damaged. The peak temperature of the package depends on package thickness and volume and is classified in accordance with <a href="Table 7">Table 7</a> and <a href="Each 2">8</a>

Table 7. SnPb eutectic process (from J-STD-020D)

| Package thickness (mm) | Package reflow temperature (°C) |       |  |  |  |  |  |

|------------------------|---------------------------------|-------|--|--|--|--|--|

|                        | Volume (mm³)                    |       |  |  |  |  |  |

|                        | < 350                           | ≥ 350 |  |  |  |  |  |

| < 2.5                  | 235                             | 220   |  |  |  |  |  |

| ≥ 2.5                  | 220                             | 220   |  |  |  |  |  |

Table 8. Lead-free process (from J-STD-020D)

| Package thickness (mm) | Package reflow temperature (°C) |             |        |  |

|------------------------|---------------------------------|-------------|--------|--|

|                        | Volume (mm³)                    |             |        |  |

|                        | < 350                           | 350 to 2000 | > 2000 |  |

| < 1.6                  | 260                             | 260         | 260    |  |

| 1.6 to 2.5             | 260                             | 250         | 245    |  |

| > 2.5                  | 250                             | 245         | 245    |  |

Moisture sensitivity precautions, as indicated on the packing, must be respected at all times.

Studies have shown that small packages reach higher temperatures during reflow soldering, see Figure 18.

# Level translating I<sup>2</sup>C-bus repeater

For further information on temperature profiles, refer to Application Note *AN10365* "Surface mount reflow soldering description".

# 14. Abbreviations

Table 9. Abbreviations

| Acronym              | Description                             |  |

|----------------------|-----------------------------------------|--|

| ВОМ                  | Bill Of Materials                       |  |

| CDM                  | Charged-Device Model                    |  |

| CMOS                 | Complementary Metal-Oxide Semiconductor |  |

| EOL                  | End Of Life                             |  |

| ESD                  | ElectroStatic Discharge                 |  |

| HBM                  | Human Body Model                        |  |

| I <sup>2</sup> C-bus | Inter Integrated Circuit bus            |  |

| I/O                  | Input/Output                            |  |

| RC                   | Resistor-Capacitor network              |  |

| SMBus                | System Management Bus                   |  |

Level translating I<sup>2</sup>C-bus repeater

# 15. Revision history

#### Table 10. Revision history

| Document ID    | Release date                                                                                                                                                                                                                                                                                                                           | Data sheet status  | Change notice | Supersedes   |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------|--------------|--|

| PCA9517A v.4.1 | 20160524                                                                                                                                                                                                                                                                                                                               | Product data sheet | -             | PCA9517A v.4 |  |

| Modifications: | <ul> <li>Corrected the text in <u>Section 6 "Functional description" on page 4</u>: "When port B falls first and goes below 0.3V<sub>CC(B)</sub>" to "When port B falls first and goes below 0.4 V"; "The port B pull-down" to "The port A pull-down"; removed sentence "If the port B low voltage does not go below 0.5 V"</li> </ul> |                    |               |              |  |

| PCA9517A v.4   | 20120509                                                                                                                                                                                                                                                                                                                               | Product data sheet | -             | PCA9517A v.3 |  |

| Modifications: | <ul> <li>Table 1 "PCA9517 and PCA9517A comparison":</li> <li>Table note [1] is rewritten</li> <li>Table 2 "Ordering information"</li> <li>Added type number PCA9517ADP/DG</li> <li>Added Table note [2]</li> <li>Figure 3 "Pin configuration for TSSOP8 (MSOP8)": added type number PCA9517ADP/DG</li> </ul>                           |                    |               |              |  |

| PCA9517A v.3   | 20120229                                                                                                                                                                                                                                                                                                                               | Product data sheet | -             | PCA9517A v.2 |  |

| PCA9517A v.2   | 20080505                                                                                                                                                                                                                                                                                                                               | Product data sheet | -             | PCA9517A v.1 |  |

| PCA9517A v.1   | 20080222                                                                                                                                                                                                                                                                                                                               | Product data sheet | -             | -            |  |

#### Level translating I<sup>2</sup>C-bus repeater

# 16. Legal information

#### 16.1 Data sheet status

| Document status[1][2]          | Product status[3]                                                                   | Definition                                                                            |

|--------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development                                                                         | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | sheet Qualification This document contains data from the preliminary specification. |                                                                                       |

| Product [short] data sheet     |                                                                                     | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

#### 16.2 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### 16.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

PCA9517A

All information provided in this document is subject to legal disclaimers.